With PowerVia, Intel Achieves a Chipmaking Breakthrough

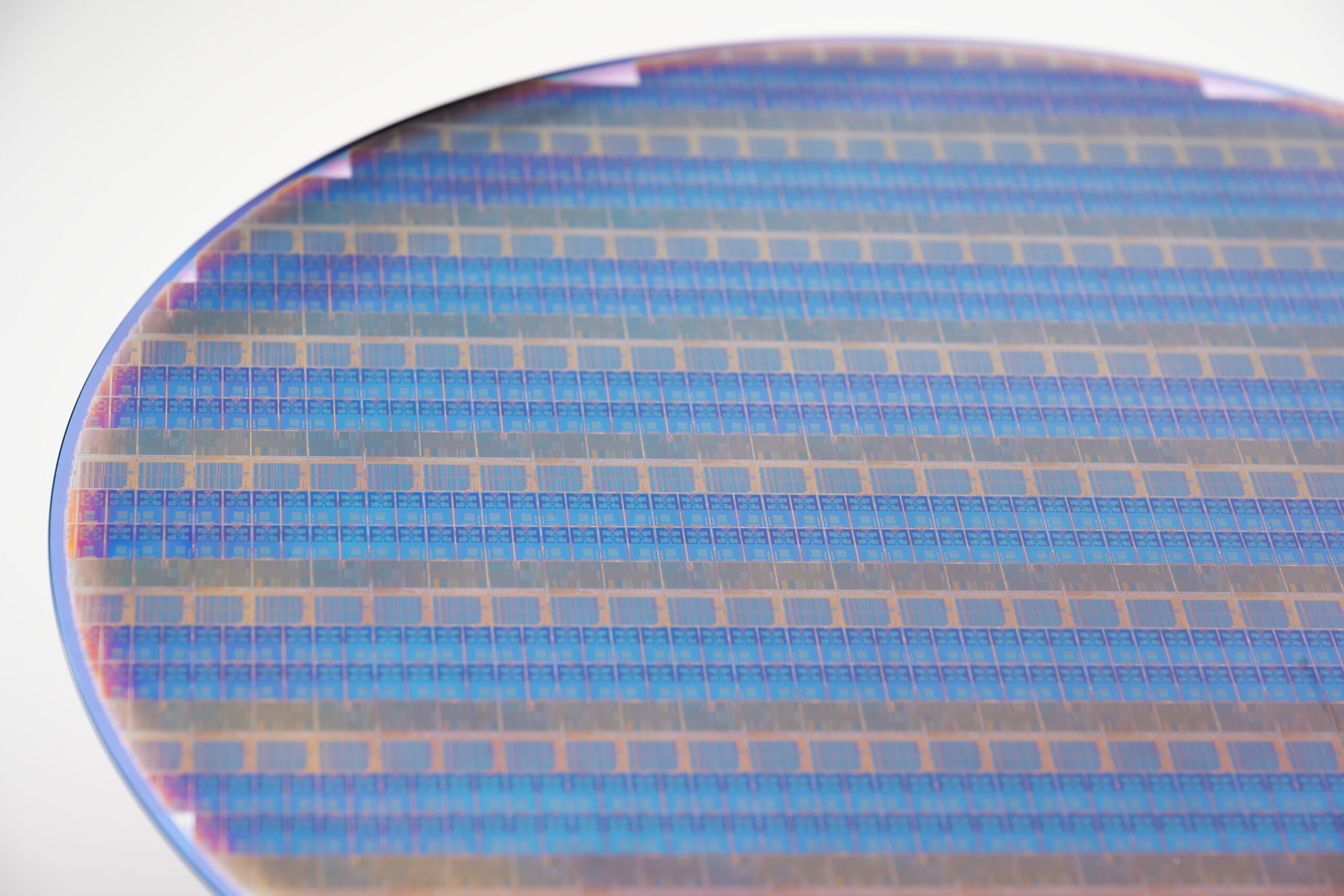

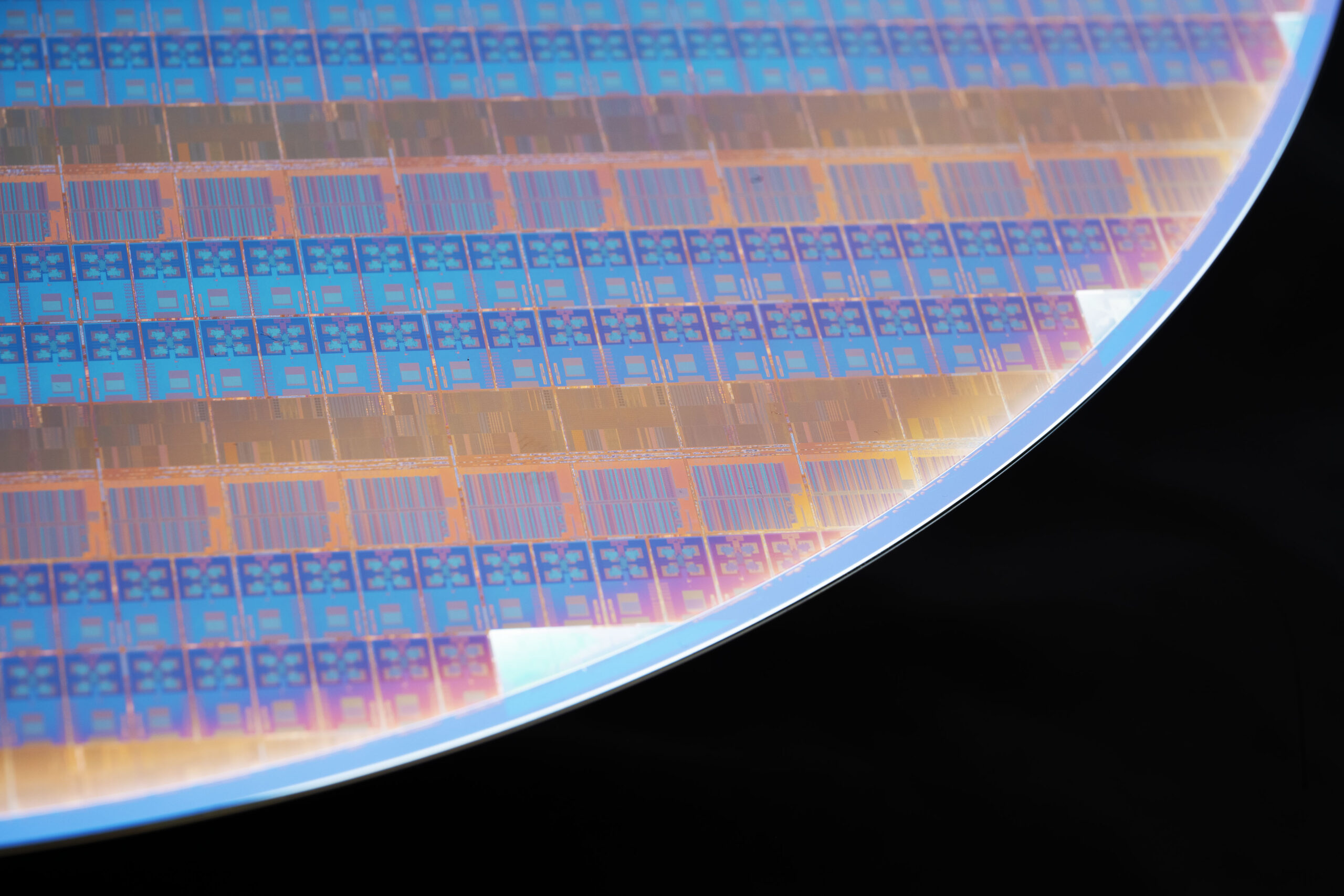

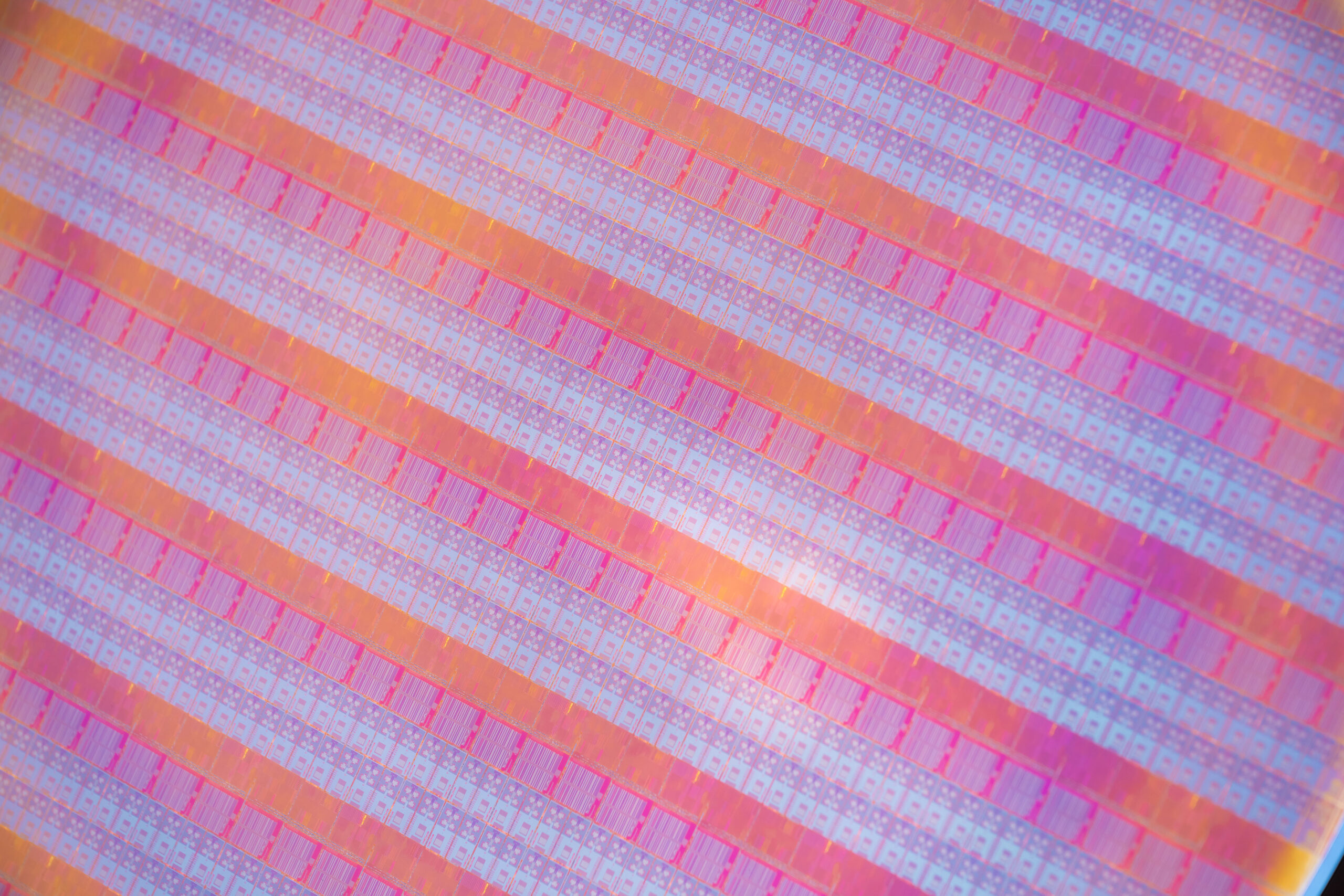

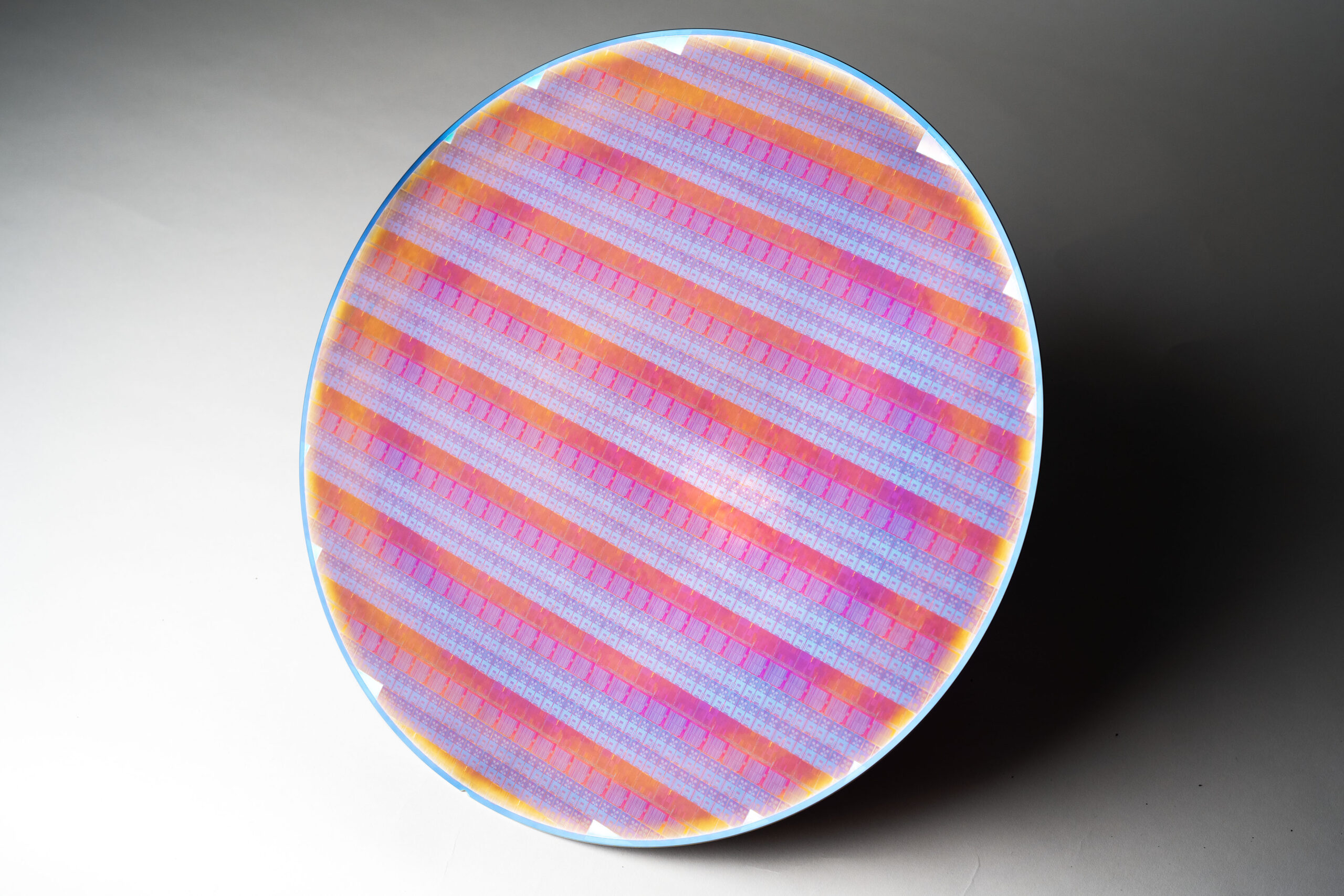

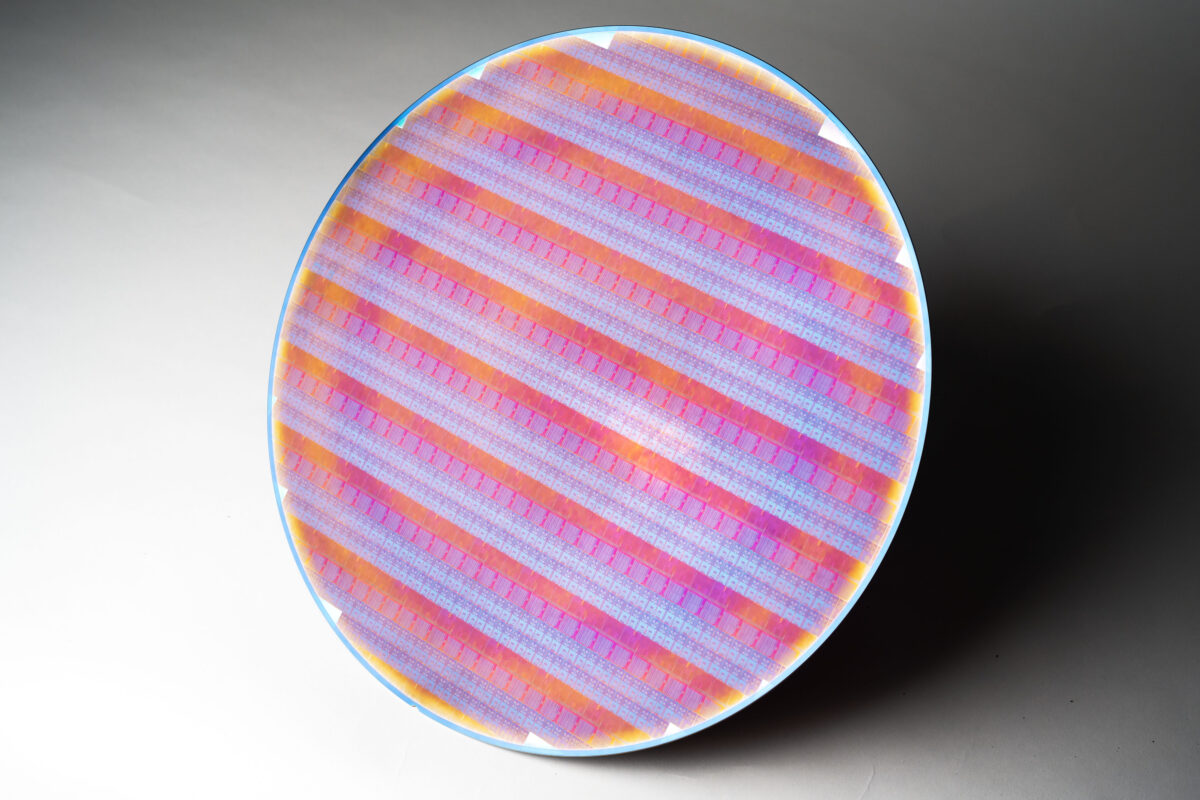

A wafer holds Blue Sky Creek test chips. The production test helps Intel refine Intel’s PowerVia backside power technology. Expected as part of the Intel 20A manufacturing node in 2024, PowerVia will be the industry’s first implementation of backside power in silicon, solving decades of interconnect bottlenecks. (Credit: Intel Corporation)

Intel’s Ben Sell explains how the company developed and proved the world's first backside power solution, taking a major step forward in chipmaking.

Intel is about to turn chipmaking upside down with PowerVia, a new approach to delivering power that required a radical rethink to both how chips are made and how they are tested.

For all the modern history of computer chips, they’ve been built like pizzas — from the bottom up, in layers. In the case of chips, you start with the tiniest features, the transistors, and then you build up increasingly less-tiny layers of wires that connect the transistors and different parts of the chip (these are called interconnects). Included among those top layers are the wires that bring in the power that makes the chip go.

When the chip is done, you flip it over, enclose it in packaging that provides connections to the outer world, and you’re ready to put it in a computer.

More: PowerVia Test Shows Industry-Leading Performance

Unfortunately, this approach is running into problems. As they get smaller and denser, the layers that share interconnects and power connections have become an increasingly chaotic web that hinders the overall performance of each chip.

Once an afterthought, “now they have a huge impact,” says Ben Sell, vice president of Technology Development at Intel and part of the team that brought PowerVia to fruition. In short, power and signals fade, requiring workarounds or simply dumping more power in.

Download all images (4.9 MB)

Two Problems, One Solution and ‘a Lot of Concerns and Hesitancy’

That’s not to say Intel teams didn’t foresee these issues — research and development on a new approach dates back a decade — nor does Intel face them alone. The solution that Intel and leading-edge chipmakers are all working toward is called “backside power,” to find a way to move the power wires below the transistor to the “back” side of the chip and thus leave the interconnect or “front” side cleanly focused only on interconnection.

Seems pretty obvious, right? Why didn’t we always do it this way? Two simple reasons: The old way is more straightforward to make and, as noted, it mostly wasn’t an issue.

But Intel’s got it figured out.

Intel’s backside power solution is called PowerVia, and two new papers to be published at the 2023 VLSI Symposium show that Intel devised a process to manufacture it, test it and demonstrate positive performance results. The “test it” part is most important, but the manufacturing part is what’s most surprising. Throw out pizza-making. For the first time, chipmaking is going two-sided.

Here’s how it works: Transistors are built first, as before, with the interconnect layers added next. Now the fun part: flip over the wafer and “polish everything off,” Sell notes, to expose the bottom layer to which the wires (well, metal layers … all these “wires” are microscopic) for power will be connected. “We call it silicon technology,” he adds, “but the amount of silicon that’s left on these wafers is really tiny.”

After the polish, “now you only have very few metal layers and they’re all very thick,” Sell explains — remember he lives in the land of nanometers, so “thick” means mere micrometers. That leaves “a very direct path for the power delivery to your transistor.”

Cost, Performance and Power Benefits Outstrip Complexity

The benefits of this approach are manifold, Sell confirms, surpassing the added complexity of the new process.

The wires for power, for example, can take up to 20% of that front-side real estate, so with them gone, the interconnect layers can be “relaxed.” “That more than offsets the cost of this whole big process,” Sell notes, simplifying what had been the most tortuous portion of the manufacturing flow. The net effect is that the two-part flip-it-over process is actually cheaper than the old way.

The benefits aren’t limited to manufacturing. The test chip the Intel team used to prove out the approach — called Blue Sky Creek and based on the Efficient-core (E-core) coming in Intel’s forthcoming Meteor Lake processor for PCs — demonstrated that PowerVia solved both problems caused by the old pizza method. With separated and fatter wires for power and interconnection, “you get better power delivery and you get better signal wiring.”

For your average computer user, this means more efficient speed. Get work done faster and with less power, the promise of Moore’s Law delivered again. As the second paper dryly concludes, “The Intel E-core designed with PowerVia demonstrates >5% frequency improvement and >90% cell density with acceptable debug times as Intel 4.” Sell confirms this is a “substantial” frequency boost for just moving wires around.

A Unique Test Chip with Intentional, Hidden Bugs

The last part of that conclusion — “acceptable debug times” — is a critical achievement alongside the product improvements. Today, chip-testing techniques are based on the accessibility of the transistors in that first and lowest layer. With the transistors now sandwiched in the middle of the chip, “a lot of those techniques had to be redeveloped,” says Sell.

“There were a lot of concerns and hesitancy and that was probably the hardest thing to figure out — how to do debug on this new backside power delivery.” To make things even more challenging, the test chip design team intentionally added some “Easter egg” errors to the chip, unbeknownst to the validation team. The good news? They found the bugs.

“We have made tremendous progress over the last couple of years in developing those debug capabilities and proving them on Blue Sky Creek,” Sell asserts.

That brings up one more novel thing about how Sell and the Intel team figured out the PowerVia recipe. PowerVia will be introduced into Intel-manufactured silicon starting with the Intel 20A node, which enters production in 2024 (Intel 20A will also see the introduction of a new gate-all-around transistor design called RibbonFET; customers of Intel Foundry Services can benefit from both innovations in the subsequent Intel 18A node, arriving later in 2024). To isolate the development of PowerVia, they took the well-proven transistors from the preceding Intel 4 process node and built a special in-between node with the power and interconnect design planned for Intel 20A.

A Special Test Process Node to Isolate Backside Power

And while Intel manufacturing and design teams regularly create all manner of Frankenstein test-chips — to test new designs and intellectual properties and to solidify silicon processes — they don’t usually make them as functional and complete as Blue Sky Creek. In this case, the teams needed to verify not only that they could build and test a chip this way, but also that the new configuration wouldn’t bring new issues into the final product.

For instance, heat. “Normally you use the silicon side also for heat dissipation,” Sell explains. “So now you have sandwiched your transistors and the question is, ‘Do we have a thermal problem? Do we get a lot of local heating?’” At this point you can probably guess the answer: no.

“What was most amazing,” Sell recalls, “was despite these radical changes” — sandwiching transistors in the middle of the chip and introducing this heavy “polishing” to the process — “we could make the transistors look very, very close to what we had in Intel 4.”

As for PowerVia, it has no peer. According to recent reports, Intel’s planned 2024 introduction of PowerVia would put competitors “roughly two years behind” when it comes to backside power.

“At least for this time period,” confirms Sell, “we have a quite competitive backside power delivery option.”

Your first opportunity to feel the many benefits of PowerVia will come next year in the form of Arrow Lake, a next-generation Intel processor for PCs built using the Intel 20A process. Its billions of transistors will be inverted, working more efficiently than ever.