Con PowerVia, Intel logra un gran avance en la fabricación de chips

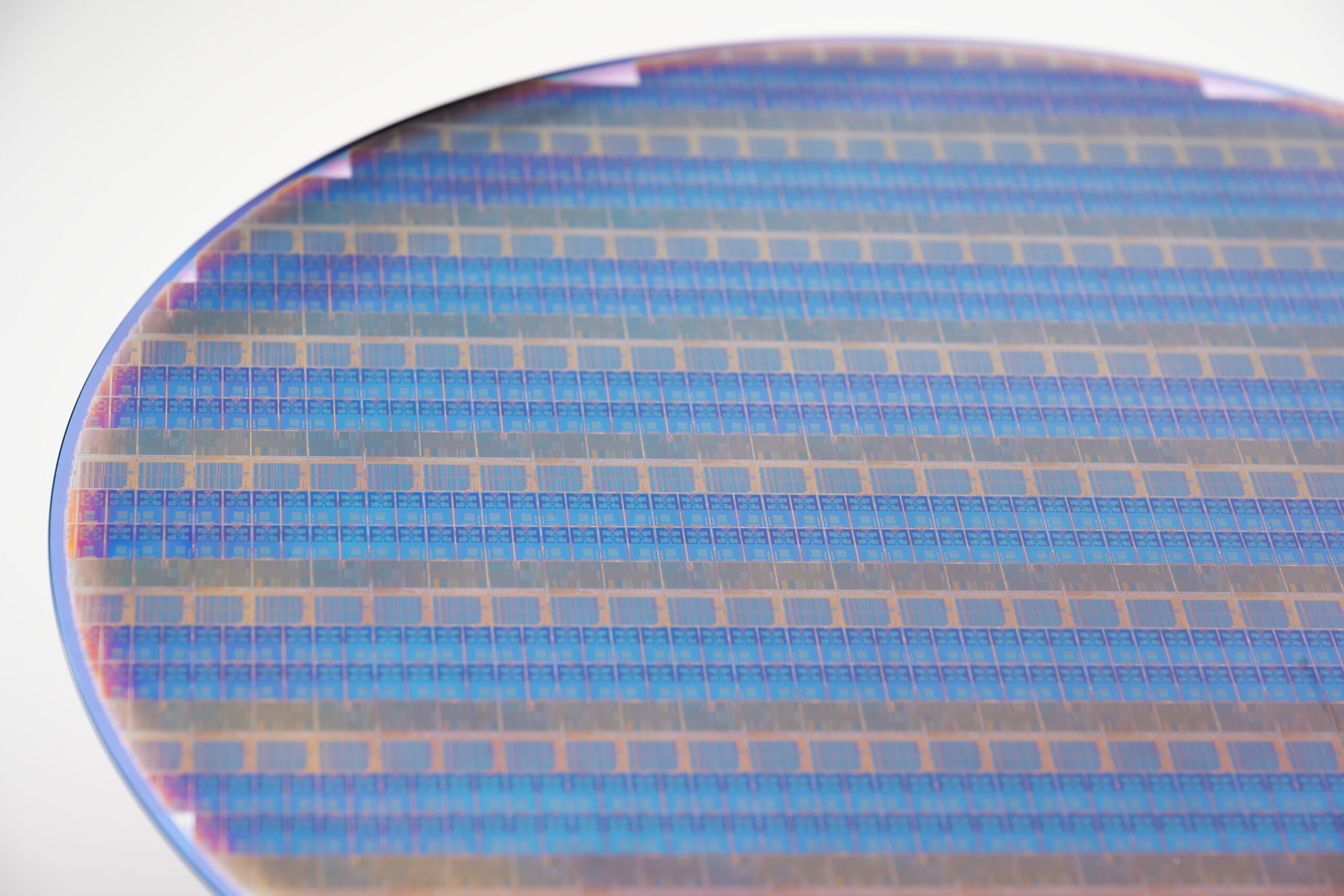

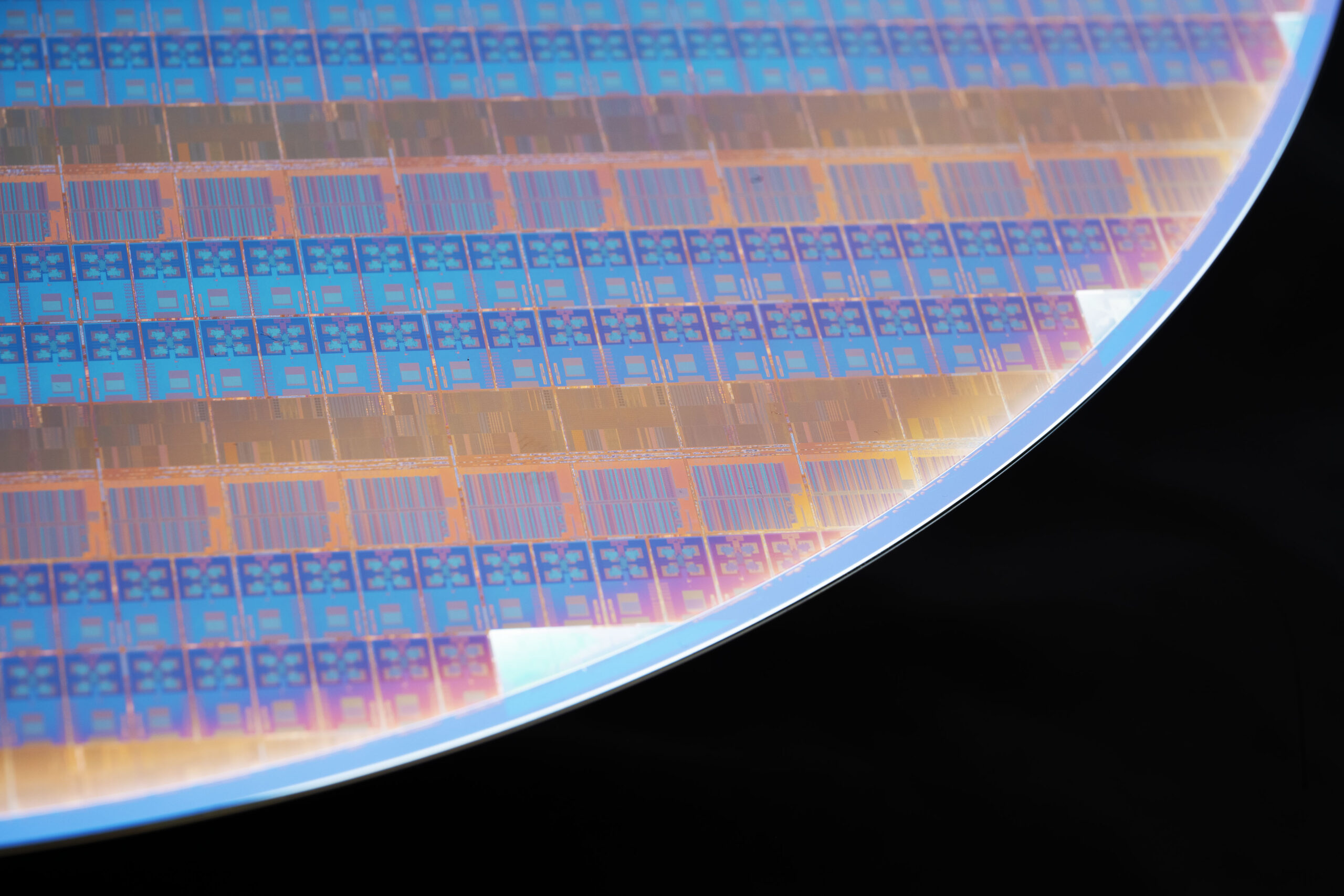

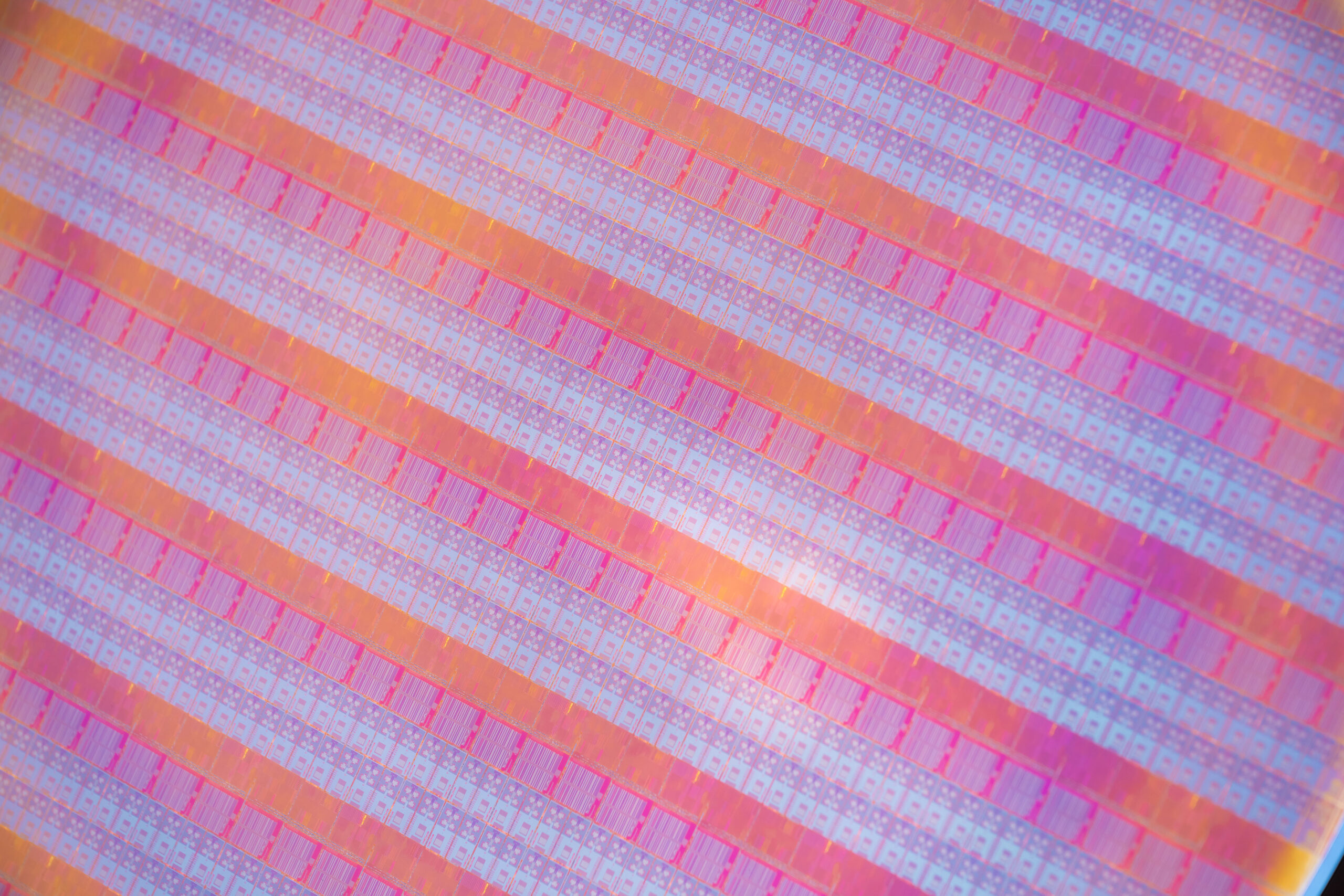

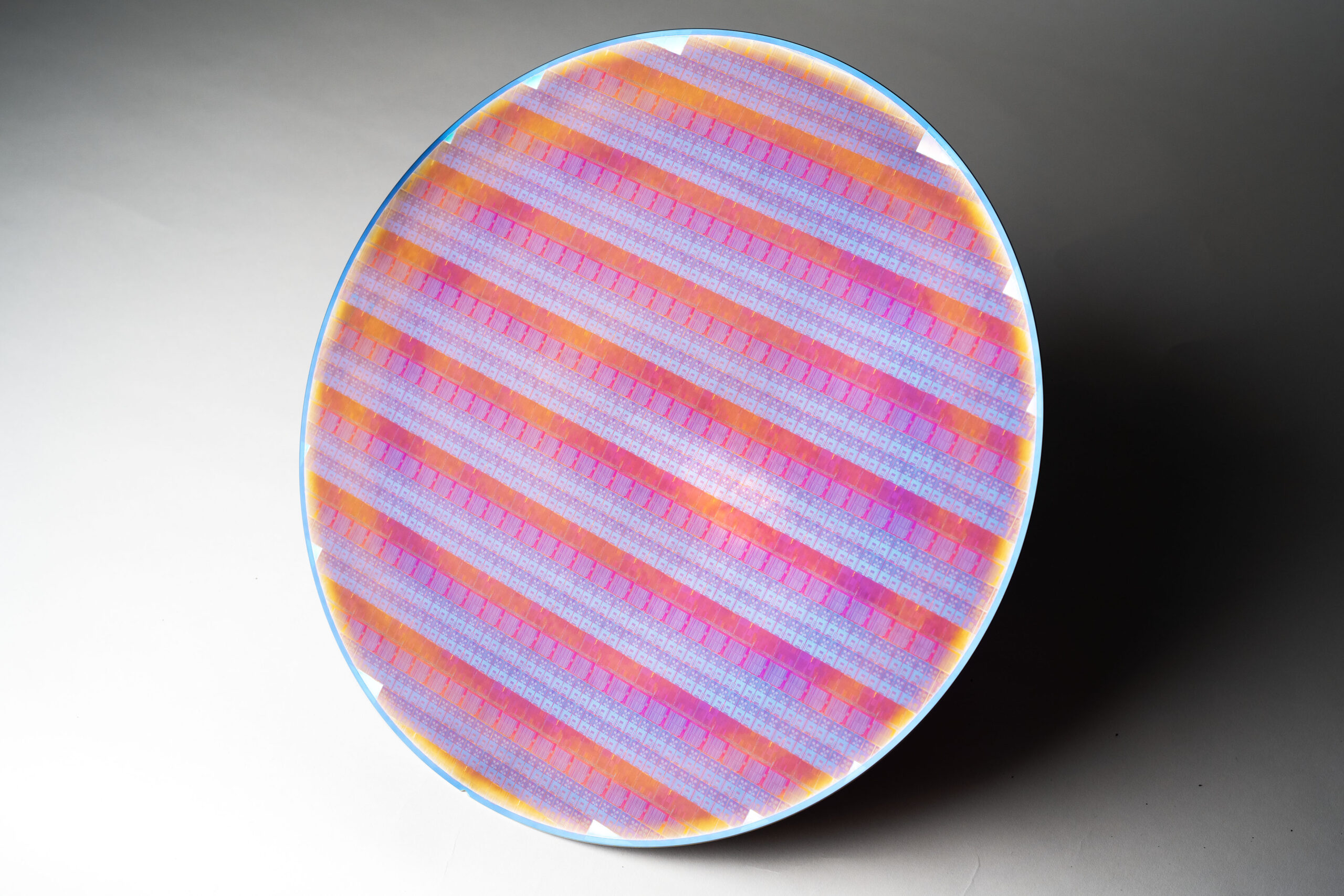

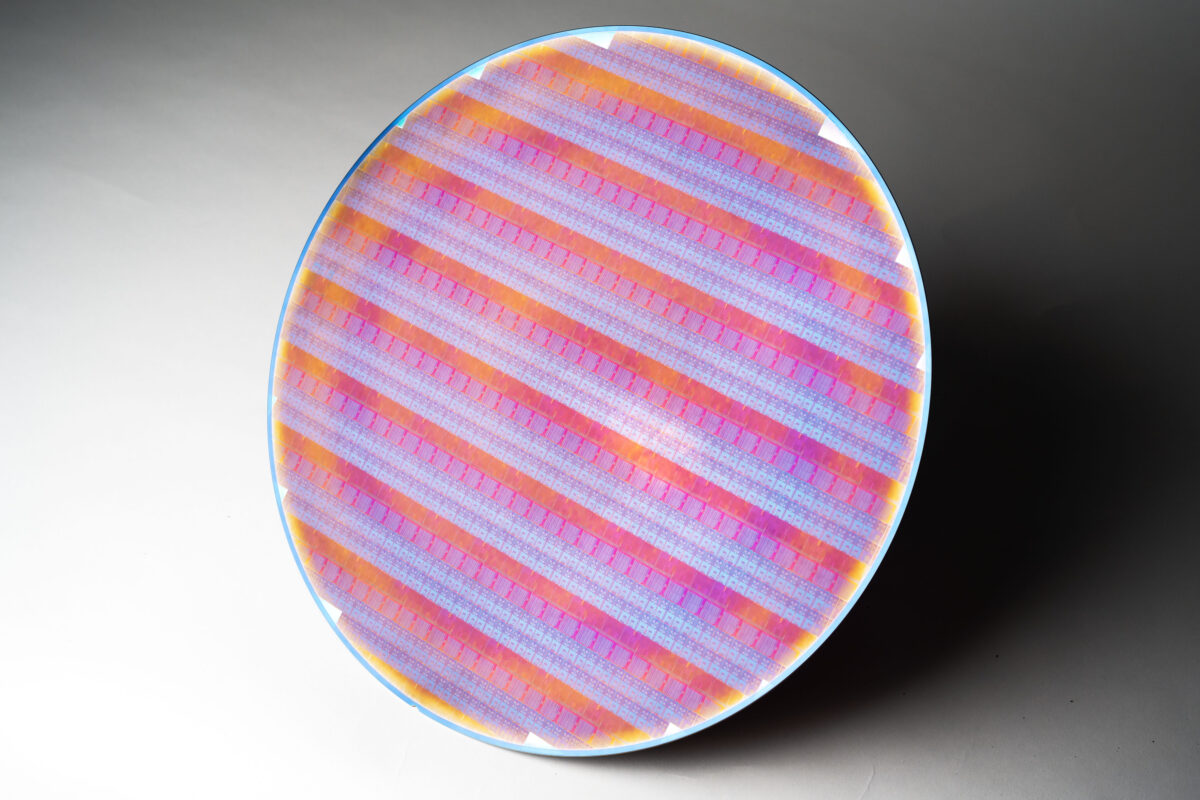

A wafer holds Blue Sky Creek test chips. The production test helps Intel refine Intel’s PowerVia backside power technology. Expected as part of the Intel 20A manufacturing node in 2024, PowerVia will be the industry’s first implementation of backside power in silicon, solving decades of interconnect bottlenecks. (Credit: Intel Corporation)

Ben Sell de Intel explica cómo la compañía desarrolló y probó la primera solución de energía backside del mundo, dando un gran paso adelante en la fabricación de chips.

Intel está a punto de revolucionar la fabricación de chips con PowerVia, un nuevo enfoque para brindar potencia que requirió un replanteamiento radical tanto de cómo se fabrican los chips como de cómo se prueban.

Durante toda la historia moderna de los chips de computadora, se han construido como pizzas, de abajo hacia arriba, en capas. En el caso de los chips, comienzas con las características más pequeñas, los transistores, y luego construyes capas de cables cada vez menos diminutas que conectan los transistores y las diferentes partes del chip (estos se llaman interconexiones). Los cables que traen la energía que hace que el chip funcione están incluidos entre esas capas superiores.

Cuando el chip está listo, lo volteas, lo encierras en un paquete que proporciona conexiones con el mundo exterior y estás listo para ponerlo en una computadora.

Más:La prueba de PowerVia muestra un desempeño líder en la industria

Lamentablemente, este enfoque está teniendo problemas. A medida que se van volviendo más pequeñas y densas, las capas que comparten interconexiones y conexiones de energía se han convertido en una red cada vez más caótica que dificulta el rendimiento general de cada chip.

En un principio se consideraban una idea aislada pero 'ahora tienen una enorme repercusión', afirma Ben Sell, vicepresidente de Desarrollo Tecnológico en Intel y parte del equipo que hizo realidad PowerVia. En resumen, la energía y las señales desaparecen, lo que requiere soluciones alternativas o simplemente la descarga de más energía.

Descargar todas las imágenes (4,9 MB)

Dos problemas, una solución y "muchas preocupaciones y dudas"

Eso no quiere decir que los equipos de Intel no hayan previsto estos problemas (la investigación y el desarrollo de un nuevo enfoque se remonta a una década), ni que los enfrente solo. La solución en la que están trabajando Intel y los fabricantes de chips de vanguardia se llama "energía backside", enfocada en encontrar una manera de mover los cables de alimentación debajo del transistor al lado "trasero" del chip y así dejar el "frente" enfocado solo en la interconexión.

Parece bastante evidente, ¿verdad? ¿Por qué no lo hacemos siempre de esta manera? Dos sencillas razones: La forma antigua es más sencilla de hacer y, como se señaló, en su mayoría no fue un problema.

Pero Intel lo tiene resuelto.

La solución de energía en la parte posterior de Intel se llama PowerVia y dos nuevos artículos que se publicarán en el 2023 Congreso VLSI muestran que Intel ideó un proceso para fabricarlo, probarlo y demostrar resultados de rendimiento positivos. La parte de "poner a prueba" es más importante, pero la pieza de fabricación es la más sorprendente. Deja de lado el "proceso de pizza" Por primera vez, la fabricación de chips tiene dos caras.

Así es como funciona: los transistores se construyen primero, como antes, y las capas de interconexión se agregan a continuación. Ahora la parte divertida: voltear la oblea y "pulir todo", señala Sell, para exponer la capa inferior a la que se conectarán los cables (bueno, capas de metal... todos estos "cables" son microscópicos) para la alimentación. "Lo llamamos tecnología de silicio", agrega, "pero la cantidad de silicio que queda en estas obleas es muy pequeña".

Después del pulido, "ahora solo tienes muy pocas capas de metal y todas son muy gruesas", explica Sell. Recuerda que vive en la tierra de los nanómetros, por lo que "grueso" significa micrómetros. Eso deja "un camino muy directo para la entrega de energía a su transistor".

Los beneficios de costo, rendimiento y energía superan la complejidad

Los beneficios de este enfoque son múltiples, confirma Sell, superando la complejidad adicional del nuevo proceso.

Los cables de alimentación, por ejemplo, pueden ocupar hasta el 20 % de ese espacio en la parte frontal, por lo que, sin ellos, las capas de interconexión pueden "relajarse". “Eso compensa con creces el costo de todo este gran proceso”, señala Sell, simplificando lo que había sido la parte más compleja de la fabricación. El efecto neto es que el proceso de voltearlo en dos partes es en realidad más barato que el método anterior.

Los beneficios no se limitan a la fabricación. El chip de prueba que utilizó el equipo de Intel para demostrar el enfoque - llamado Blue Sky Creek y basado en el núcleo eficiente (E-core) que viene en el próximo procesador Meteor Lake de Intel para PCs - demuestra que PowerVia resolvió ambos problemas causados por el antiguo "método de pizza". Con cables separados y más gruesos para la alimentación y la interconexión, "obtiene una mejor entrega de energía y un mejor cableado de señal".

Para el usuario promedio de una computadora, esto significa una velocidad más eficiente. Hace el trabajo más rápido y con menos energía. La promesa de la Ley de Moore se cumplió nuevamente. Como concluye el segundo documento, "El intel E-core diseñado con PowerVia demuestra un >5 % de mejora de frecuencia y >90 % de densidad celular con tiempos de depuración aceptables como Intel 4". Sell confirma que se trata de un aumento de frecuencia "sustancial" para solo mover cables.

Un chip de prueba único con errores intencionales ocultos

La última parte de esa conclusión, "tiempos de depuración aceptables", es un logro fundamental junto con las mejoras del producto. Hoy en día, las técnicas de prueba de chips se basan en la accesibilidad de los transistores en esa primera capa y en la más baja. Con los transistores ahora emparedados en medio del chip, "se tuvo que reenmarcar muchas de esas técnicas", señala Sell.

“Había muchas preocupaciones y dudas, y eso fue probablemente lo más difícil de resolver: cómo depurar esta nueva entrega de energía en la parte posterior". Para hacer las cosas aún más desafiantes, el equipo de diseño de chip de prueba agregó intencionadamente algunos a modo de “Easter egg”, sin que el equipo de validación lo sepa. ¿Las buenas noticias? Encontraron los errores.

“Hemos hecho un gran progreso en los últimos años en el desarrollo de esas capacidades de depuración y demostrándolas en Blue Sky Creek”, afirma Sell.

Eso trae a colación una cosa más novedosa sobre cómo Sell y el equipo de Intel descubrieron la receta de PowerVia. PowerVia se introducirá en los chips fabricados por Intel a partir del nodo Intel 20A, que entrará en producción en 2024 (Intel 20A también verá la introducción de un nuevo diseño de transistor de compuerta integral llamado RibbonFET; los clientes de Intel Foundry Services pueden beneficiarse de ambas innovaciones en el posterior nodo Intel 18A, que llegará más adelante en 2024). Para aislar el desarrollo de PowerVia, tomaron los transistores del nodo de proceso Intel 4 anterior y construyeron un nodo intermedio especial con el diseño de alimentación e interconexión planificado para Intel 20A.

Nodo de proceso de prueba especial para aislar la energía de la parte posterior

Y aunque los equipos de fabricación y diseño de Intel crean regularmente todo tipo de chips de prueba de Frankenstein, para probar nuevos diseños y propiedades intelectuales y para solidificar los procesos de chips de silicio, por lo general no los hacen tan funcionales y completos como Blue Sky Creek. En este caso, los equipos tenían que verificar no solo que podían armar y probar un chip de esta manera, sino también que la nueva configuración no traería nuevos problemas al producto final.

Por ejemplo, el calor. “Normalmente, también usa el lado de silicona para disipar el calor”, explica Sell. “Así que ahora has intercalado sus transistores y la pregunta es: ‘¿Tenemos un problema térmico? ¿Tenemos mucha temperatura local?'" En este punto probablemente puede imaginar la respuesta: no.

“Lo más asombroso”, recuerda Sell, “fue que, a pesar de estos cambios radicales (intercalar transistores en el medio del chip e introducir este fuerte “pulido” en el proceso) podíamos hacer que los transistores se vieran muy parecidos a lo que eran en Intel 4”.

En cuanto a PowerVia, no tiene igual. Según informes recientes, la introducción de PowerVia en el 2024 planeada por Intel pondría a los competidores "aproximadamente dos años detrás" cuando se trata de potencia de backside.

"Al menos durante este período", confirma Sell, "tenemos una opción de entrega de energía de backside bastante competitiva".

Su primera oportunidad para sentir los muchos beneficios de PowerVia llegará el año próximo en forma de Arrow Lake, un procesador Intel de próxima generación para PCs diseñadas con el proceso Intel 20A. Sus miles de millones de transistores se invertirán, trabajando más eficientemente que nunca.